Миландр 1986ВЕ1Т. Проблемы с прошивкой.

Небольшая заметка о том: как решить проблему загрузки прошивки; причем здесь J-link; и как снова подружить его с Миландром

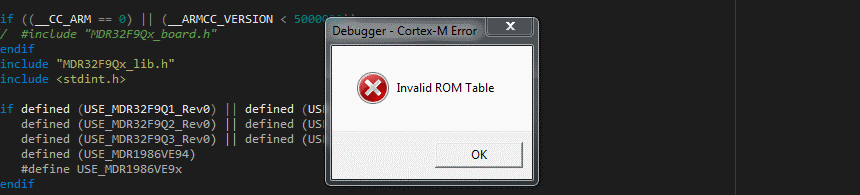

Использую последнюю версию Keil (5.25) и программатор ST-Link V2, и никогда не замечал проблем с прошивокой микроконтроллеров Миландр. Правда раньше работал только с семейством ВЕ9х (91, 92, 93) и их пластиковыми аналогами. Всё хорошо ровно до тех пор пока не добрался до ВЕ1Т. Мало того, что он на ядре которое предназначено для прошивания во всевозможные ПЛИС, так ещё и никак не хотел шиться. Постоянно выдавая ошибку Invalid ROM Table.

Отступать некуда, пришлось разобраться и решить эту проблему.

Для начала раз десять перечитал главу 8 в спецификации "Организация памяти". Вроде и значения правильные стоят, а ошибка всё равно возникает. Пречитав форум производителя так и не нашел ничего, что могло бы решить проблему, но натолктуло на интересное решение.

А написано было следующее (То, за что зацепился мой взгляд я выделил):

На данный момент микроконтроллер программируется и отлаживается с помощью ПО Keil 3 с программатором ULINK2, либо ПО Keil 4 с программатором J-link. Поэтому настоятельно рекомендуется во избежании лишних вопросов применять предложенные комбинации ПО и программатора.

Что нам это даёт если у нас в наличии только ST-Link? Строго говоря - ничего, но если немного поработать...

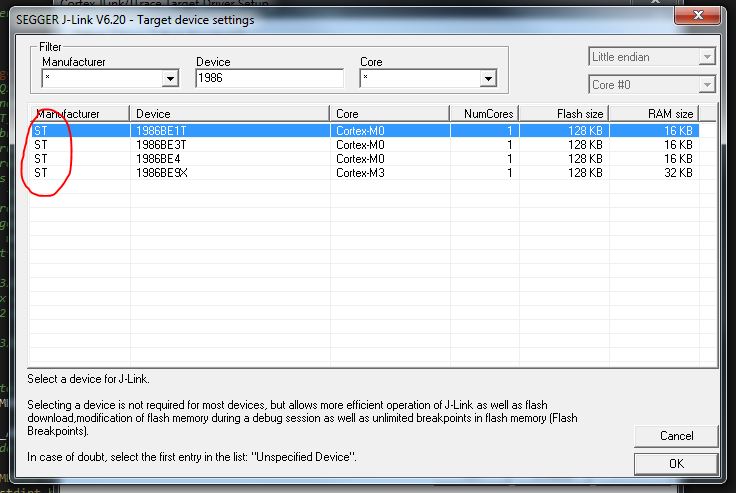

Нужно лишь перешить наш программатор в J-Link. Для этого смотрим мою заметку Превращаем ST-Link в J-Link и дружим его с Миландром.

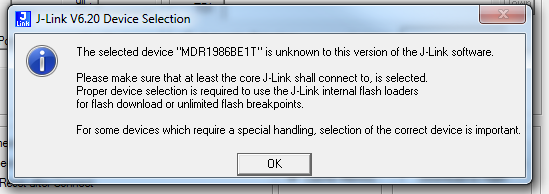

Вот только новая версия J-Link STLink не поддерживает прошивку и отладку микроконтроллеров любых других производителей кроме STMicroelectronics.

К счастью это легко обходится. Необходимо немного подкорректировать файл JLinkDevices.xml, который недавно скопировали.

Все строки вида ChipInfo Vendor="Milandr" необходимо отредактировать и привести в соответствие ChipInfo Vendor="ST"

Теперь Миландровские чипы стали СТМовскими

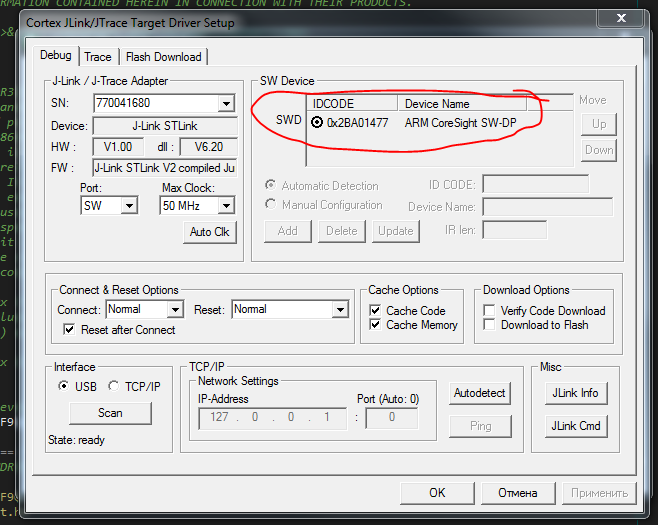

И процесс прошивки идёт как нужно

Load "D:\\03. Проекты\\Модуль сетевой\\Objects\\NetModule.axf"

* JLink Info: Device "1986BE1T" selected.

* JLink Info: Device "1986BE1T" selected.

Set JLink Project File to "D:\03. Проекты\Модуль сетевой\JLinkSettings.ini"

* JLink Info: Device "1986BE1T" selected.

JLink info:

------------

DLL: V6.20 , compiled Sep 8 2017 18:04:35

Firmware: J-Link STLink V2 compiled Jun 26 2017 10:34:41

Hardware: V1.00

S/N : 770041680

* JLink Info: Found SW-DP with ID 0x4BA01477

* JLink Info: Scanning AP map to find all available APs

* JLink Info: AP[1]: Stopped AP scan as end of AP map has been reached

* JLink Info: AP[0]: AHB-AP (IDR: 0x44770001)

* JLink Info: Iterating through AP map to find AHB-AP to use

* JLink Info: AP[0]: Core found

* JLink Info: AP[0]: AHB-AP ROM base: 0xE00FF000

* JLink Info: CPUID register: 0x411CC210. Implementer code: 0x41 (ARM)

* JLink Info: Found Cortex-M1 r1p0, Little endian.

**JLink Warning: Identified core does not match configuration. (Found: Cortex-M1, Configured: Cortex-M0)

* JLink Info: FPUnit: 4 code (BP) slots and 0 literal slots

* JLink Info: CoreSight components:

* JLink Info: ROMTbl[0] @ E00FF000

* JLink Info: ROMTbl[0][0]: E000E000, CID: 00000000, PID: 00000000 ???

* JLink Info: ROMTbl[0][1]: E0001000, CID: 00000000, PID: 00000000 ???

* JLink Info: ROMTbl[0][2]: E0002000, CID: 00000000, PID: 00000000 ???

ROMTableAddr = 0xE00FF000

* JLink Info: Reset: Halt core after reset via DEMCR.VC_CORERESET.

* JLink Info: Reset: Reset device via AIRCR.SYSRESETREQ.

Target info:

------------

Device: MDR1986BE1T

VTarget = 3.300V

State of Pins:

TCK: 0, TDI: 0, TDO: 64, TMS: 0, TRES: 1, TRST: 255

Hardware-Breakpoints: 4

Software-Breakpoints: 8192

Watchpoints: 2

JTAG speed: 4000 kHz

Full Chip Erase Done.

Programming Done.

Verify OK.

* JLink Info: Reset: Halt core after reset via DEMCR.VC_CORERESET.

* JLink Info: Reset: Reset device via AIRCR.SYSRESETREQ.

Application running ...

Flash Load finished at 13:51:41