В который раз о портах совмещенных с JTAG. STM32

Не работает PB3 на stm32f103? Тогда мы идём к вам. Расскажу как не наступить на эти грабли.

У меня была одна из заметок про подобную тему, но то был контроллер Миландр. На этот раз его собрат от компании STMicroelectronics - stm32f103rc. Необходимо было задетвовать ножки порта PB3, PB4 и PB5 - на них висит SPI1, с помощью которого планировалось управлять переферийной микросхемой.

Проблемы кроются в деталях. Оказалось, что запустить SPI, так и не получится, косяк в разводке - перепутаны дата и клок, выкрутимся "ногодрыгом", но это другая история.

То, что ноги совмещены с JTAG означает, что нужно сделать ремап, то есть отключить функцию JTAG для этих выводов. Что и было сделано и вроде всё должно работать как часики.

Если интересно, то отключение с помощью SPL делается так:

RCC_APB2PeriphClockCmd( RCC_APB2Periph_AFIO, ENABLE );

GPIO_PinRemapConfig (GPIO_Remap_SWJ_JTAGDisable, ENABLE );C помощью CMSIS вот так:

AFIO->MAPR |= AFIO_MAPR_SWJ_CFG_JTAGDISABLE;Самое интересное началось после. Получилось так, что все необходимые выводы кроме PB3 функционируют нормально, а он всё время находится в состоянии логической единицы (3,3 В на выводе).

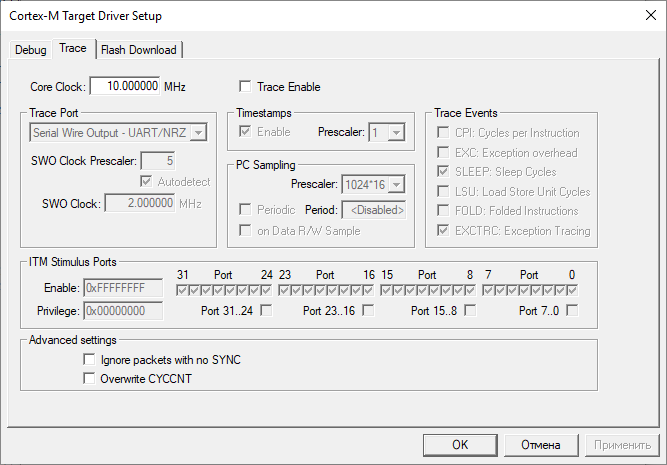

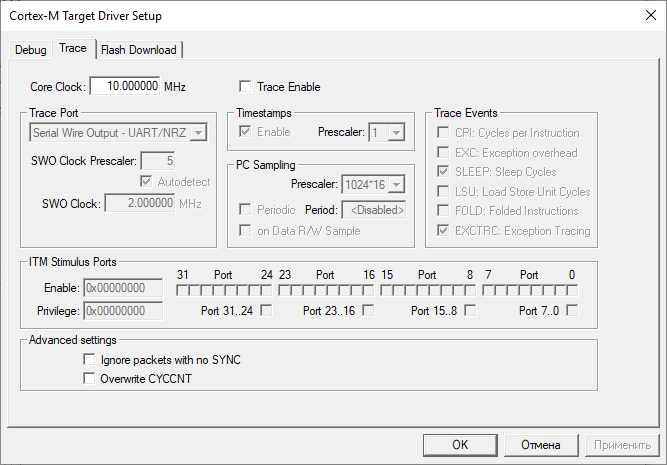

В голову полезли мысли, что процессу мешает SWD интерфейс, ведь этот вывод не что иное как SWO сигнал. Но в мануале на чип ясно сказано, что не должен мешать если не используется асинхронная трассировка, а она действительно не используется. Вот настройки ST-Link в Keil:

Прикол в том, что даже если трассировака выключена, отладчик все равно задействует этот канал. Что бы наверняка издавиться от этой проблемы нужно включить трассировку и поснимать галочки в поле ITM Stimusus Ports, или что намного проще в поле Enable ввести значение 0x0 и затем снова отключить трассировку.

Как бы это не было парадоксально, но это работает. По крайней мере с ST-Link это именно так.